swiss scientific initiative in health / security / environment systems

## Placitus FNSNF **RTD 2010**

# **Complementary BAW oscillators for Ultra-Low Power Consumption and Low Phase Noise**

Raghavasimhan Thirunarayanan and Christian Enz

Centre Suisse d'Electronique et de Microtechnique, CSEM SA, Neuchâtel, Switzerland

École polytechnique fédérale de Lausanne, EPFL, Lausanne, Switzerland

A complementary cross coupled BAW parallel resonance oscillator offering ultra-low power consumption and a good phase noise performance is presented. The power consumption in this structure is 50% less than the classical NMOS based structure without any penalty in the phase noise performance. Rather, this structure serves to reduce the noise contribution of the biasing transistors at the output leading to a marginal improvement in thermal noise performance as compared to the NMOS based structure. Furthermore, the flicker noise upconversion of this complementary structure can be minimized by proper design.

## **Complementary BAW oscillators**

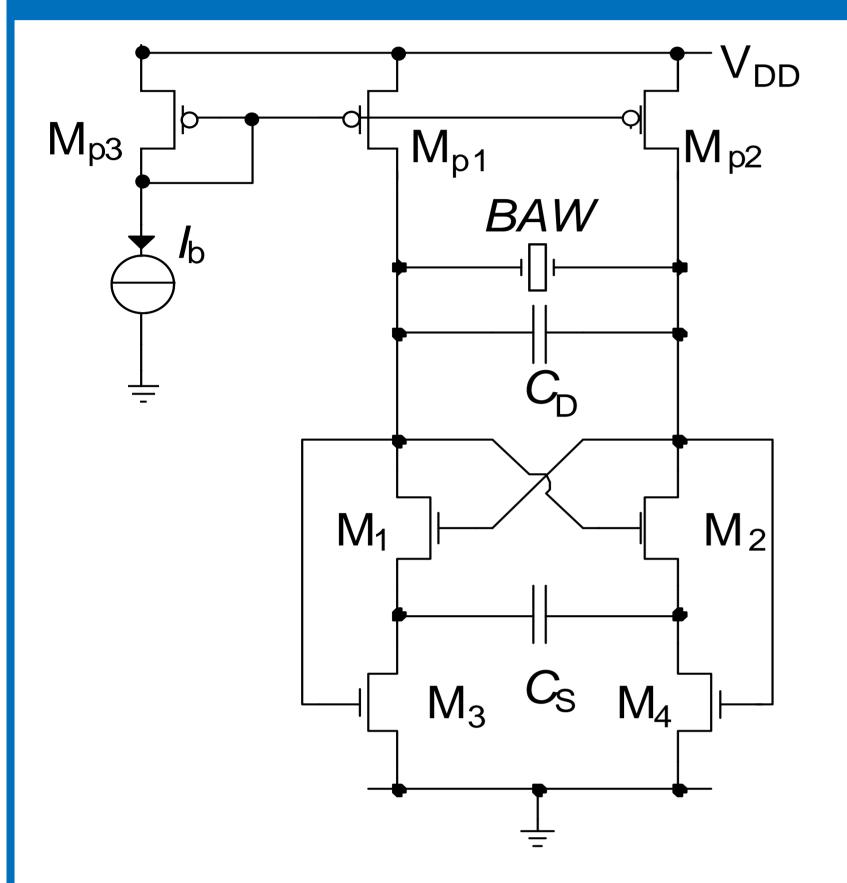

NMOS CROSS-COUPLED (C-C) BAW OSCILLATOR

#### POWER CONSUMPTION

The power consumption in weak inversion  $P = \kappa \cdot V_{DD} \cdot 2G_{mcrit} \cdot nU_T$

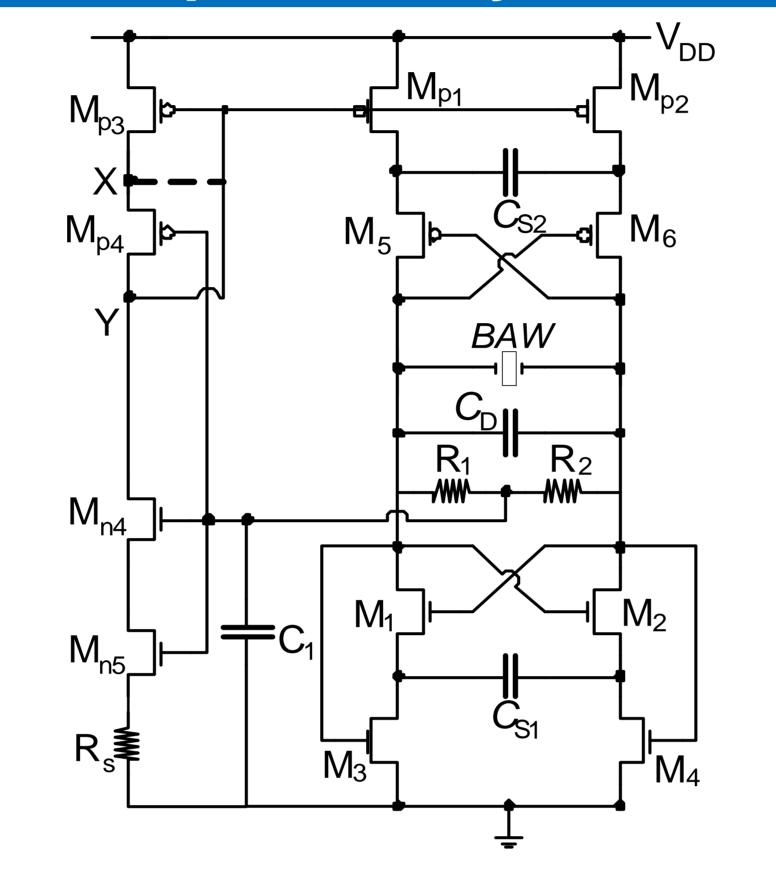

**COMPLEMENTARY BAW OSCILLATOR**

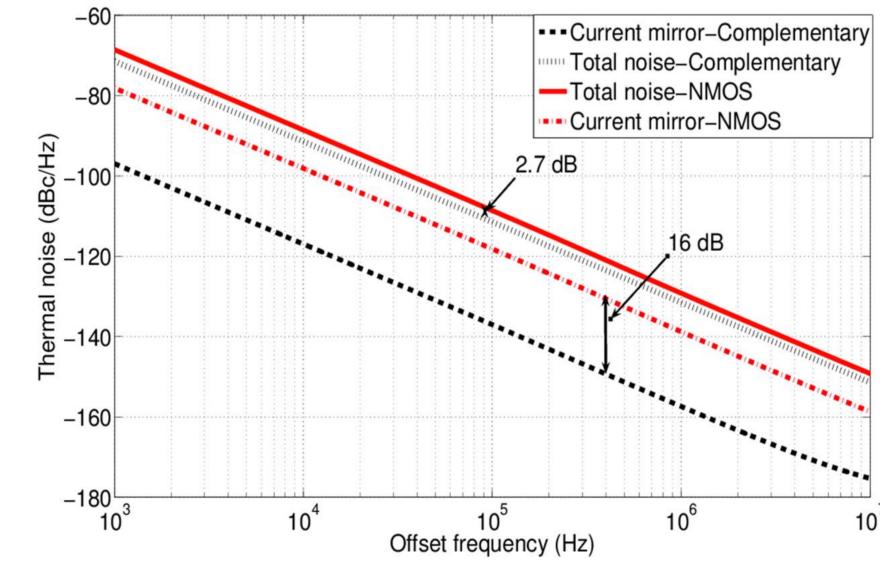

#### THERMAL NOISE

Total Noise of the cross coupled (c-c) pair - approx. same for same amplitude for NMOS c-c and complementary structures. Noise of the CMFB transistors - negligible in both cases.

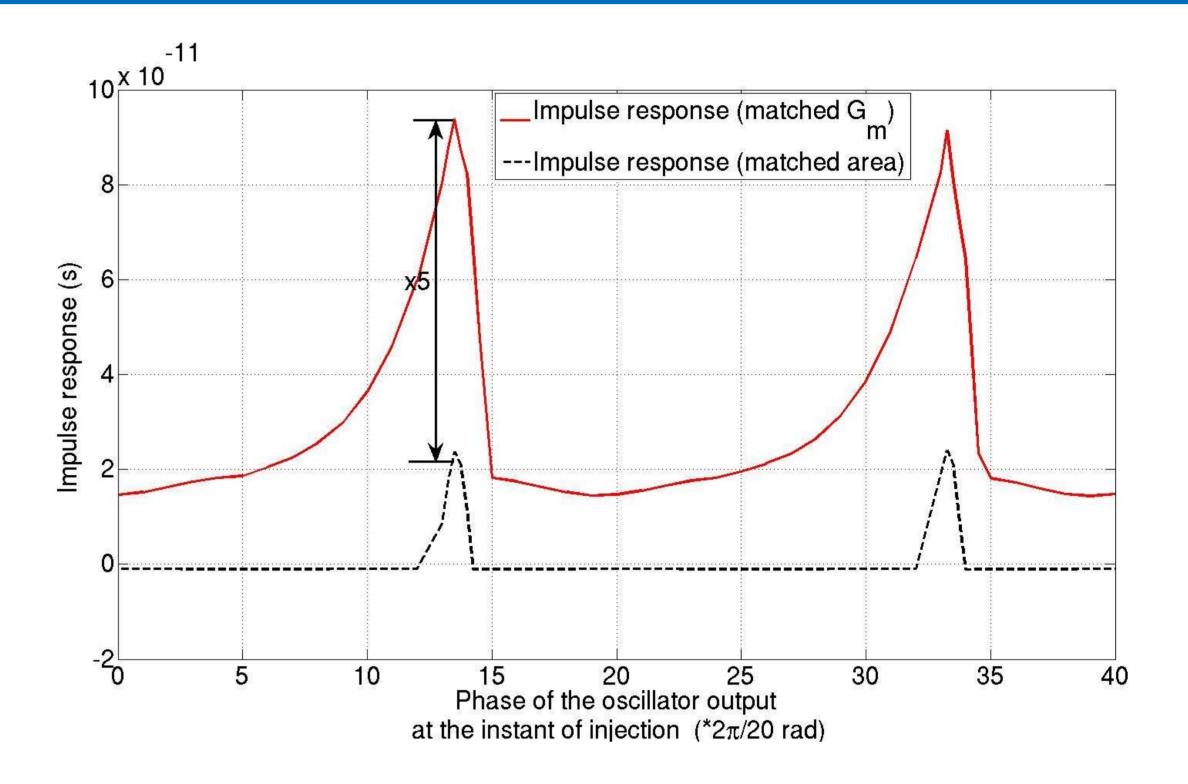

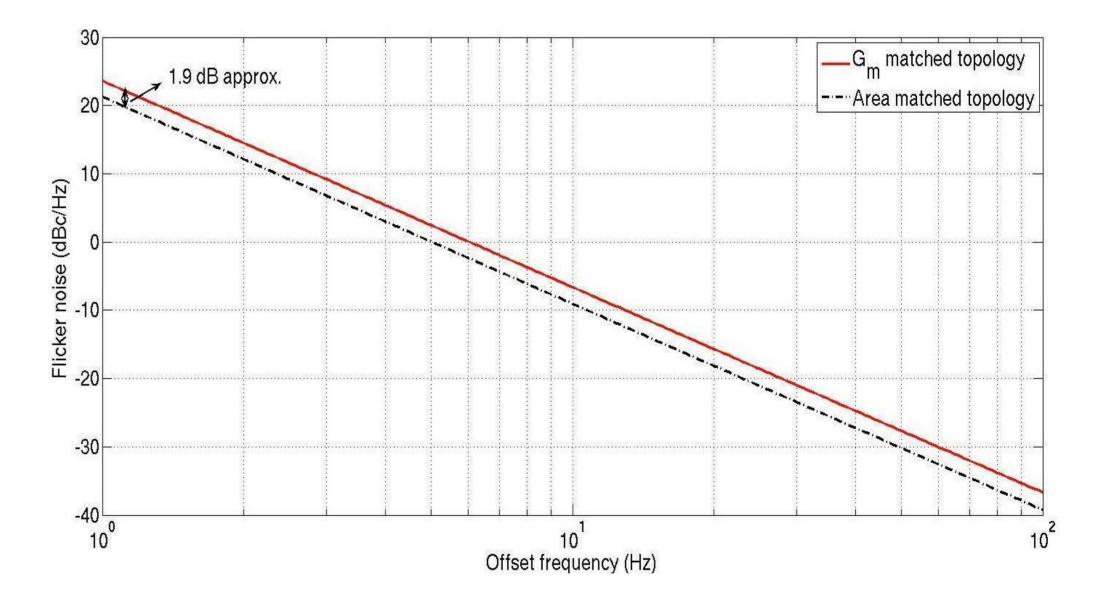

**ISF COMPARISON – Gm MATCHED VS AREA MATCHED TOPOLOGIES**

### FLICKER NOISE

Biasing Complementary structuretransistor not connected to output unlike NMOS c-c structure.

- Complementary structure:  $G_{mcrit} = R_m C_L^2 \omega_0^2$

- NMOS c-c structure:  $G_{mcrit} = 2R_m C_L^2 \omega_0^2$

- So, ideally :  $P_{complementary} = \frac{1}{2} P_{NMOS}$ for same output signal amplitude.

BAW

- Noise from the current mirror negligible for the complementary structure.

- The total noise at the output is lower for the complementary structure due to an increase in load capacitance

i.e. Phase noise  $\alpha \frac{1}{C_{LOAD}^2}$

- Sizes of these transistors can be increased to reduce their flicker noise without increasing power.

- Complementary structure : Optimization of flicker noise Matching between the NMOS and PMOS c-c pair (Match in area / Match in G<sub>m</sub>).

- Impulse sensitivity Function (ISF) simulation shows that c-c pair area-matched topology has the best flicker noise performance.

## **Results & Conclusions**

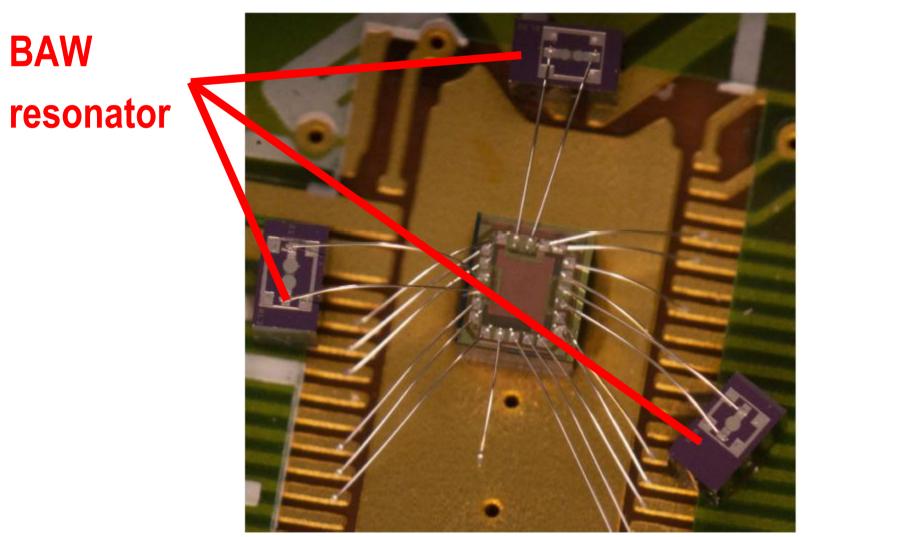

**MICROPHOTOGRAPH OF THE CHIP**

**THERMAL NOISE COMPARISON –**

FLICKER NOISE COMPARISON -

#### **Gm MATCHED VS AREA MATCHED TOPOLOGIES**

|                   | Complementary      | NMOS based         |

|-------------------|--------------------|--------------------|

|                   | structure          | structure          |

| Frequency         | $2.537 \ GHz$      | $2.545 \ GHz$      |

| Power Consump-    | $667.5 \ \mu W$    | $1177.5 \ \mu W$   |

| tion              |                    |                    |

| Flicker Noise @ 1 | $21.18 \ dBc/Hz$   | $26.278 \ dBc/Hz$  |

| Hz offset         |                    |                    |

| FOM @ 1 Hz off-   | $105.585 \ dB$     | $96.07 \ dB$       |

| set               |                    |                    |

| Thermal Noise @   | $-119.02 \ dBc/Hz$ | $-115.87 \ dBc/Hz$ |

| 100 kHz offset    |                    |                    |

| FOM @ 100 kHz     | $194.03 \ dB$      | $188.425 \ dB$     |

| offset            |                    |                    |

#### Conclusions

A complementary structure based BAW resonator oscillator at 2.53 GHz which consumes around 670µW power for achieving an amplitude of 300mV has been demonstrated in this work. A comparison with the NMOS based structure reveals that complementary structure has half the power consumption due to increased negative resistance at the same bias current. Further, there is a marginal improvement in the case of the latter due to better filtering of noise of biasing transistors for the same amplitude. This results in a gain of around 5dB in 1/(Power\*Phase Noise) Figure of Merit. Also, by using an area matched topology for the NMOS and the PMOS cross-coupled pairs in the complementary structure, a flicker noise performance better than that of the NMOS based structure can be achieved.

COMPLEMENTARY STRUCTURE VS NMOS **BASED STRUCTURE – PERFORMANCE**

R.Thirunarayanan, A. Heragu, D. Ruffieux, and C. Enz, NewCAS, June 2011 (Best Student Paper Award)