# 100Giga Fast Encryption Engine

O. Auberson<sup>1</sup>, G. Curchod<sup>1</sup>, Y. Graf<sup>1</sup>, E. Messerli<sup>1</sup>, L. Monat<sup>2</sup>

<sup>1</sup>HES-SO Yverdon, <sup>2</sup>idQuantique SA

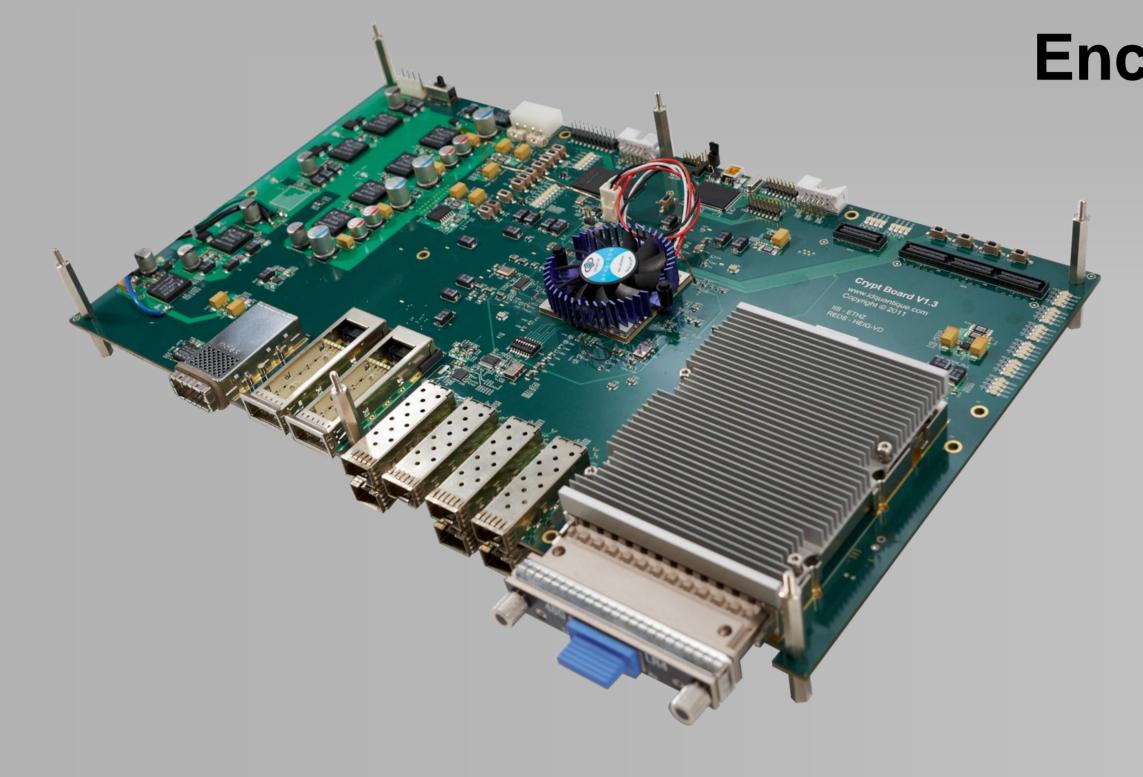

## **Encryption Engine Prototype**

We develop a next generation encryption device that can be seamlessly embedded in existing network infrastructures to provide quantum enhanced security

- High-speed serial links @ 10Giga managed in FPGA

- 10 Ethernet channels @ 10Giga

- 100 Gbps AES encryption engine

- 100 Gbps data channel over a single fiber

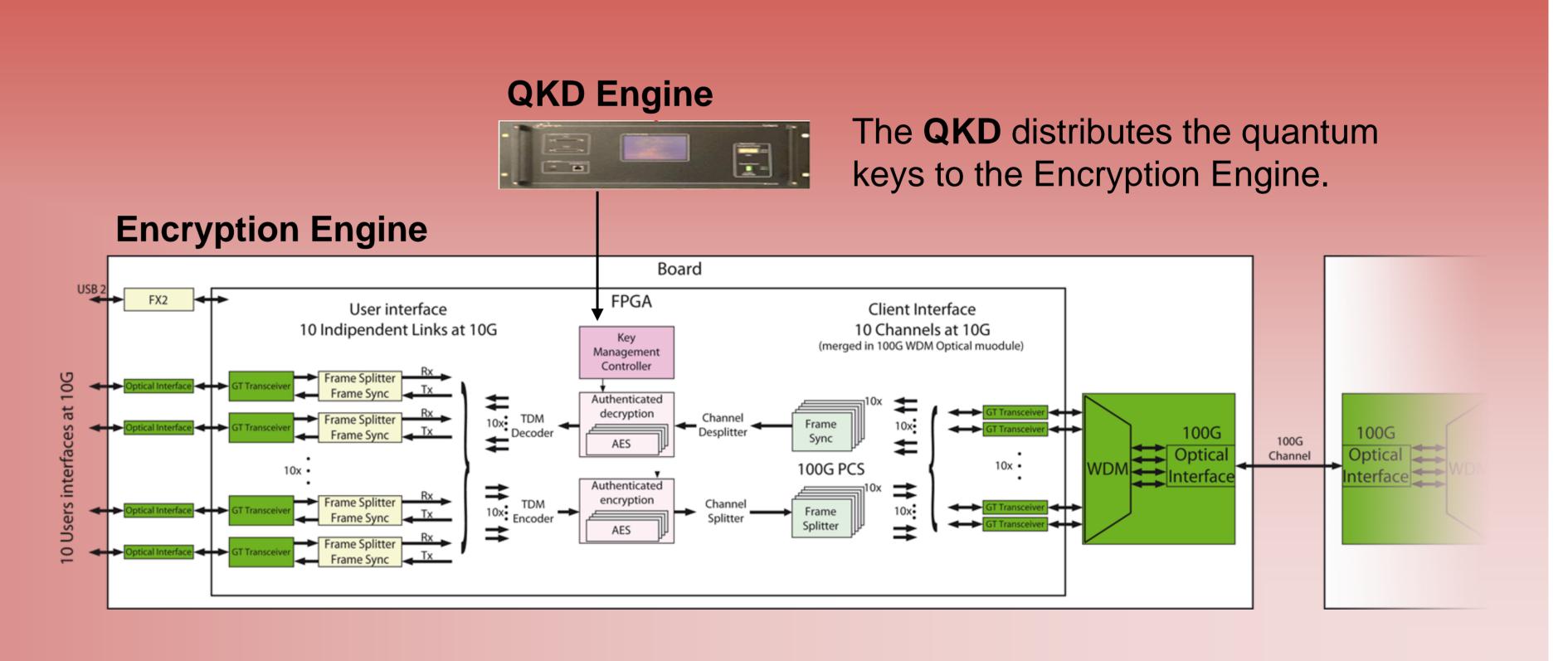

# **Encryption Design for Secure Channel**

#### **FPGA Design**

The user side receives, merges and encrypts 10 SFP+ modules @10G to one CFP module @100G on the client side.

The AES encryption uses the quantum keys distributed by the QKD Engine.

FPGA: Stratix IV GT (EP4S100G5)

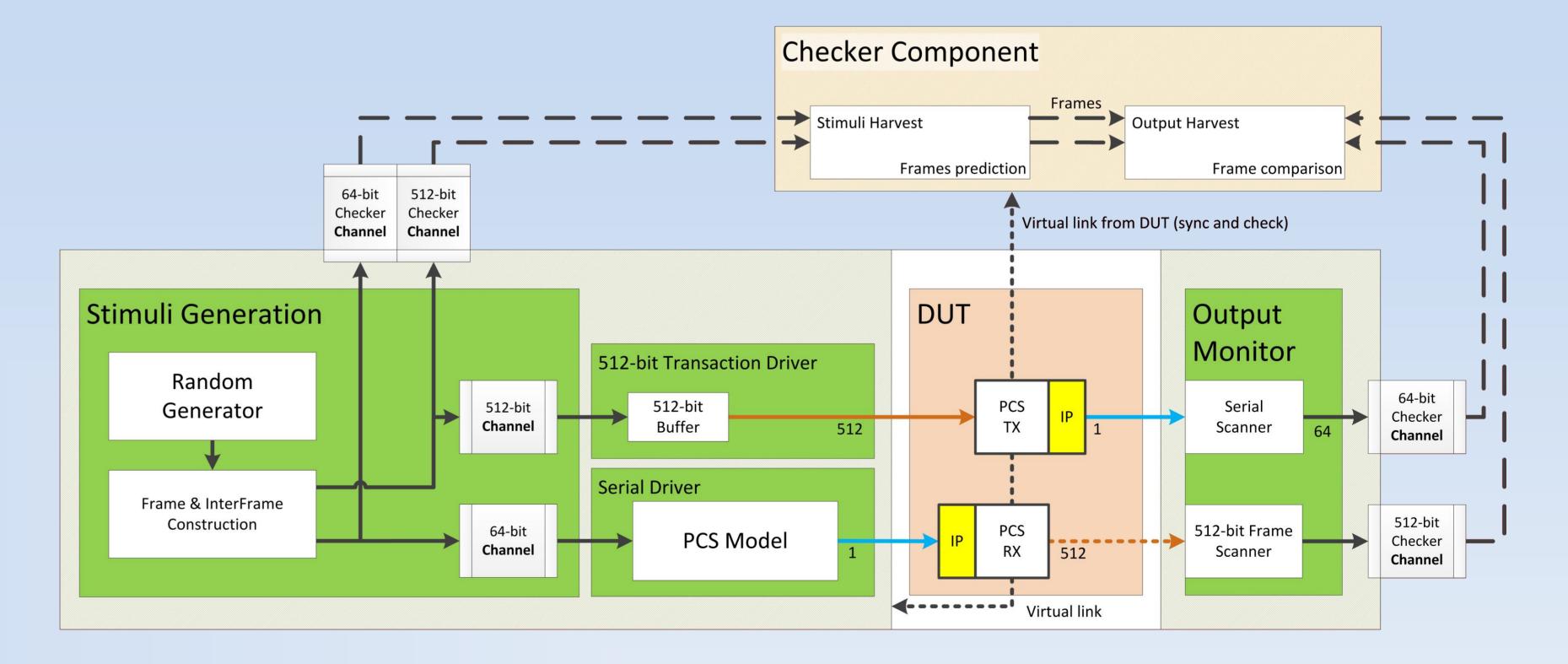

#### SystemVerilog Test Environment

#### **Testbench**

The testbench is based on the newest SystemVerilog verification framework. The latter provides several functionalities such as

- Objet-oriented;

- Random generation;

- Transaction channels.

- Verification methodologies (OVM, UVM)

### Features

- SystemVerilog Model of the 10G PCS

- Frame checker component

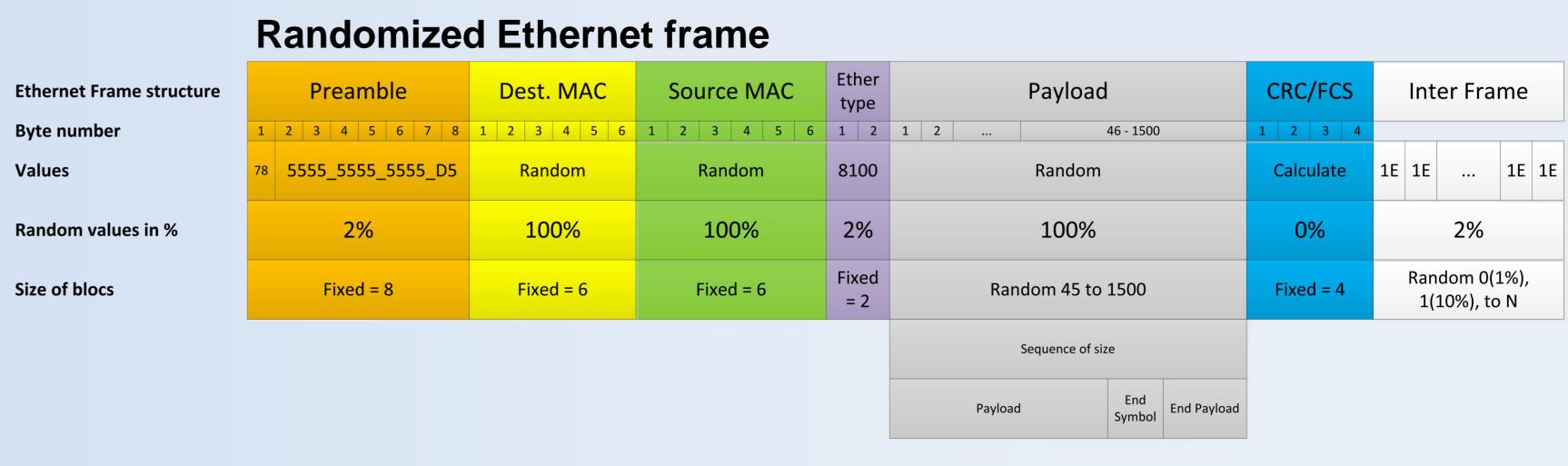

- Ethernet frame generation with random values and sizes

Principal investigator: Nicolas Gisin (Nicolas.Gisin@unige.ch)

Contact: Etienne Messerli (etienne.messerli@heig-vd.ch)

Norbert Felber (felber@iis.ee.ethz.ch)