# Intra chip stack fluidic cooling: the CMOSAIC demonstrator

Yassir Madhour<sup>1</sup>, Michail Zervas<sup>2</sup>, Brian P. D'Entremont<sup>1</sup>, Thomas Brunschwiler<sup>3</sup>, Gerd Schlottig<sup>3</sup>, Bruno Michel<sup>3</sup>, Yusuf Leblebici<sup>2</sup> and John Richard Thome<sup>1</sup>

<sup>1</sup>Heat and Mass Transfer Laboratory, Swiss Institute of Technology, EPFL LTCM, CH-1015 Lausanne, Switzerland, <sup>2</sup>Microelectronic Systems Laboratory, Swiss Institute of Technology, EPFL LSM, CH-1015 Lausanne, Switzerland, <sup>3</sup>IBM Research – Zurich, 8803 Rüschlikon, Switzerland.

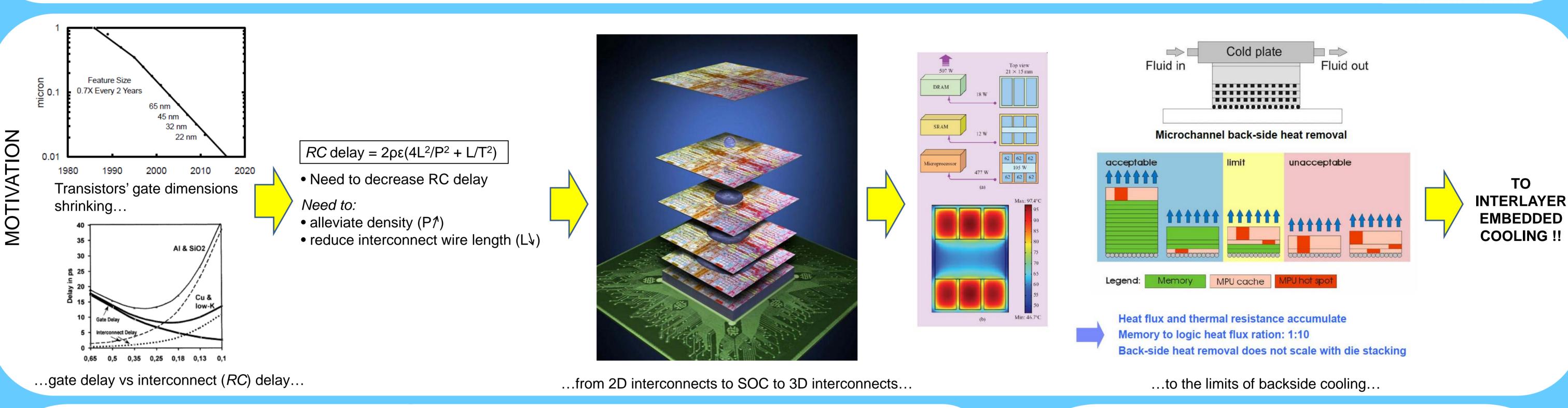

### 1<sup>st</sup> generation CMOSAIC interlayer cooling: PYRAMID STACK

- 5-layer chip stack.

- 4 active levels with layer-embedded cooling structures.

- Heat removal configurations: Silicon microchannels or Si pin fins.

- Stacking: high pressure membrane bonding.

- Polymer die-to-die bonding.

- Individual die power input through wire-bonding.

- Wedge-wedge 25µm Aluminum wires.

- RTDs on every layer for temperature measurements.

- No Through Silicon Vias.

1st generation: PYRAMID STACK

© IBM Research

#### Cavity: Junction: ---middle 7-1 4µm polyimide bond 200nm Al<sub>2</sub>O<sub>3</sub> insulation 400nm Al pad / wire 250nm Al heater / sensor 200nm SiO<sub>2</sub> insulation 425µm Si slab 100µm Si cavity

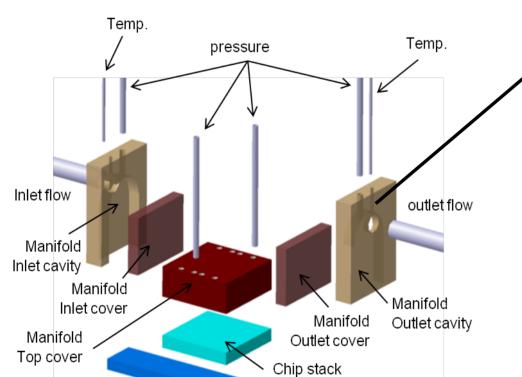

#### Experimental Heat Transfer and Package **Performance Tests**

Exploded view of the top of the package

Manifold for coolant delivery into chip stack.

Possible direct measurements during package operation:

- Accurate local pressures and temperatures of coolant fluid, inside the manifold entrance and exit cavities.

- Accurate coolant pressure drop across entire package. Accurate pressure drop across chip-level only, for 2 different levels.

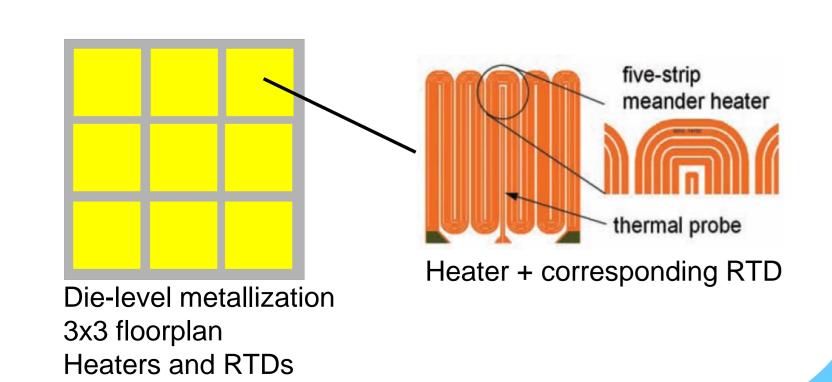

- Additional pressure and temperature (junction and coolant) via Resistance Thermal Detectors (RTDs) deposited at die-level, front side.

## A novel 3D Heat Conduction Model for chip stacks with integrated two-phase cooling

Copper TSV

# Advantages:

(\$\sqrt{3}\)

<u>></u> 2000 }

S 1500

$\begin{array}{c} 1000 \\ \text{Chan. 0} \\ y = 0 \text{ mm} \end{array}$

- Accurate, mechanistic, flow-patternbased methods for microchannel heat transfer and pressure drop.

- Heat spreading: Copper Through Silicon Vias (TSV) included.

- Resolves vertical distribution of heat and thermal resistance between Convective Resistances Adjusted for Fin Efficiency  $\overline{\phantom{a}}$ evaporators.

- Careful consideration of fin efficiency Fluid Temperature and through-conduction for the twoended fin. Allows parametric study for the placement of heat sources within the

Chan. 50 y = 10 mm

- chip stack.

- spots on each layer. • Same outlet vapor quality (33%).

• Same size, shape, and total area of hot

Over three fold increased performance due to the consideration of layer interaction effects in hot spot placement

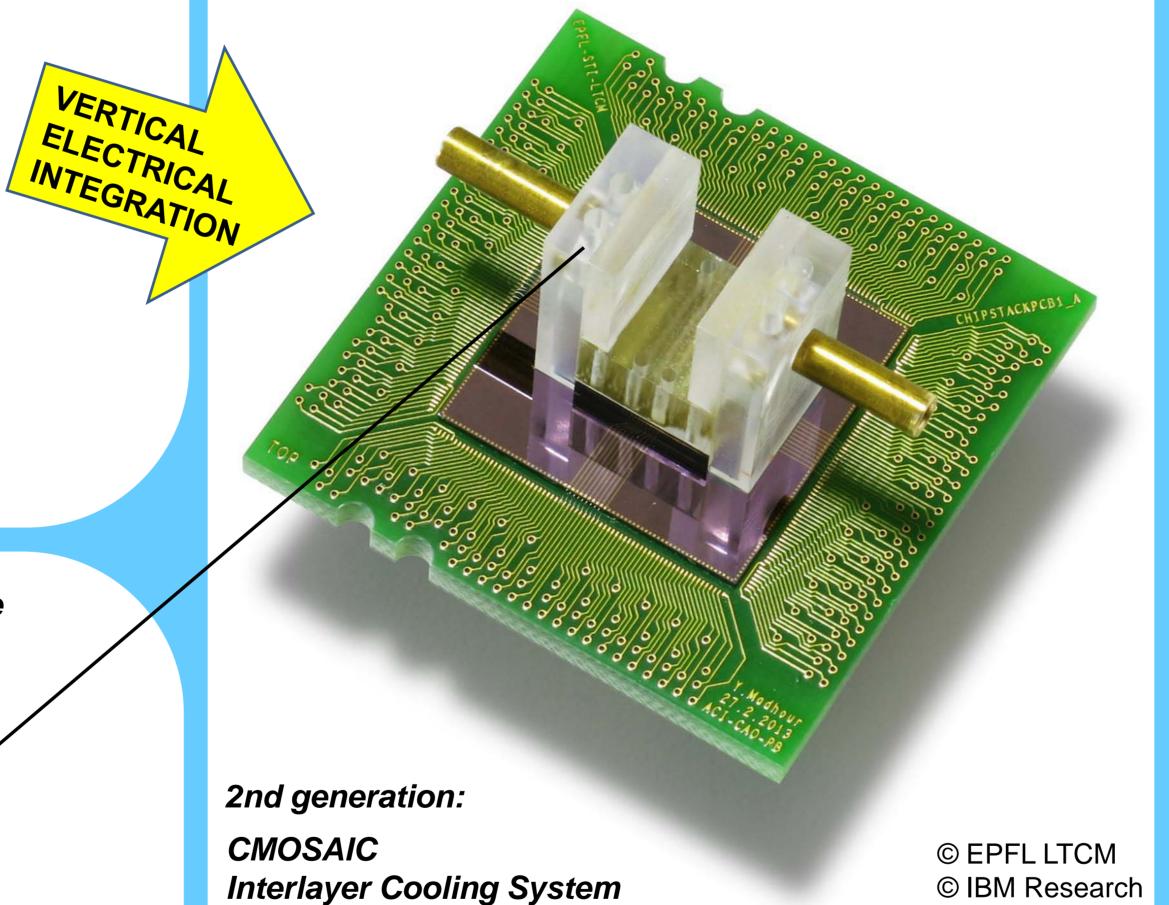

# Fabrication & Assembly

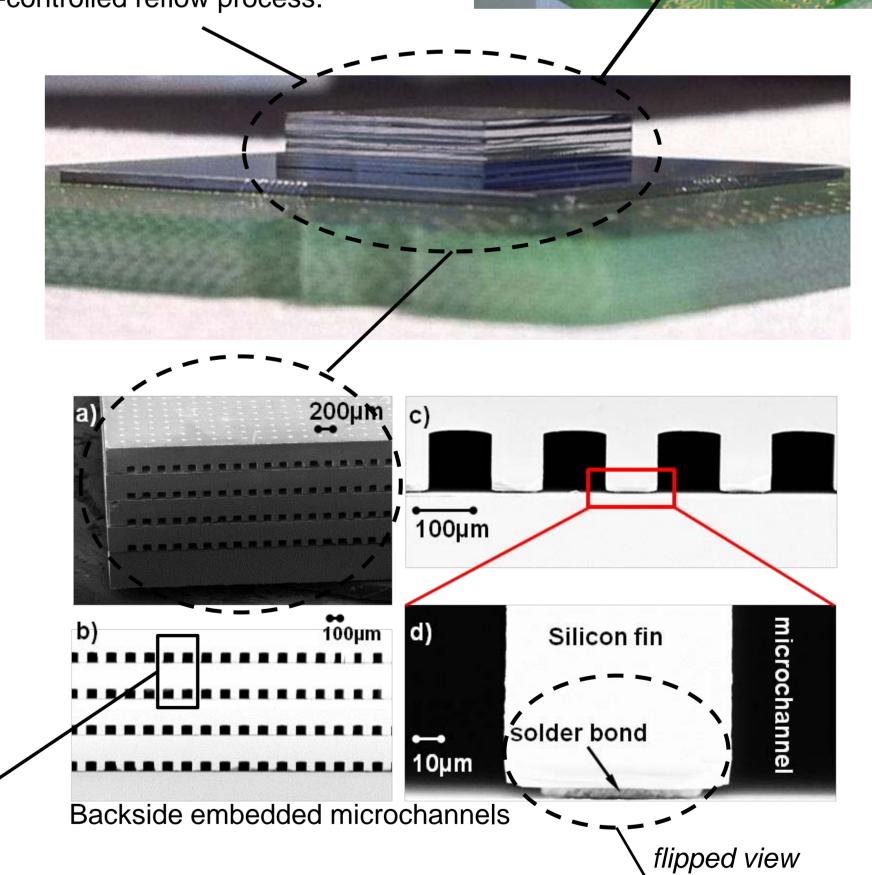

- Silicon interposer chip.

- 22x22mm.

- Interface between PCB and chip stack.

- Wedge-wedge 25µm Aluminum wire-bond.

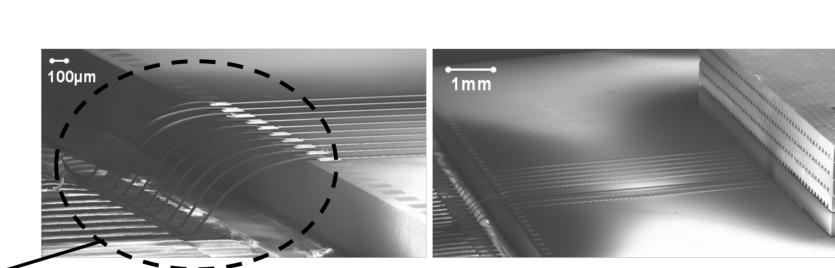

- 5 layer chip stack.

- chip stack FC bonded to interposer.

- 10x10mm chips.

- 5 electrically active layers.

- 4 layers with embedded cooling structures.

- Stacking via flip-chip (FC) solder bonding. • Force-controlled reflow process.

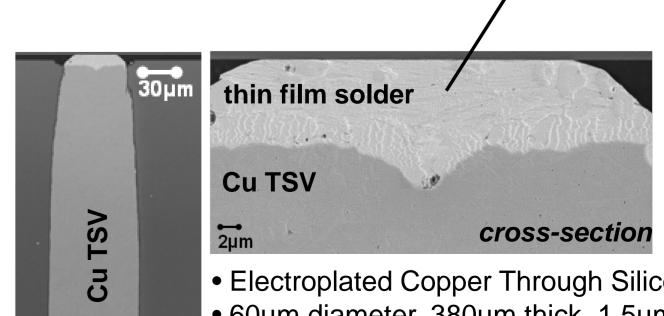

- Thin film solder.

- Electroplated on top of TSV surface.

- 58µm diameter. • 15µm thick after plating.

- 5µm thick after FC bonding.

- DRIE Silicon microchannels. • 100x100µm.

Electroplated Copper Through Silicon Vias (TSVs).

Single chip bottom view

• 60µm diameter, 380µm thick, 1.5µm oxide insulation. • 53x63 floorplan per die, > 3000 TSVs per chip.

Acknowledgements: Ute Drechsler, Ralph Heller, Walter Riess, Chris Sciacca, Richard Stutz, Martin Witzig.