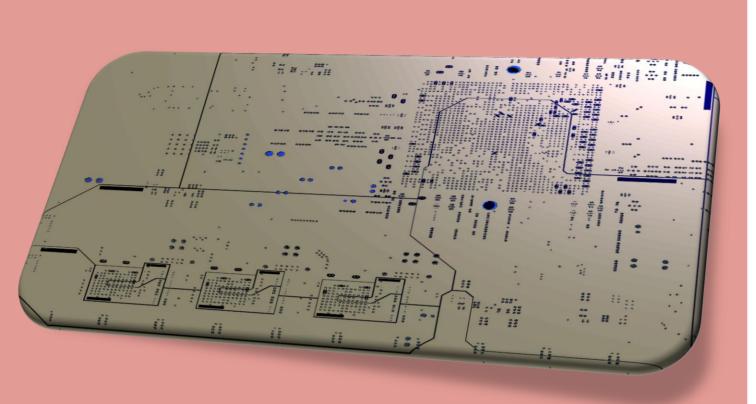

Stackup PCB V2

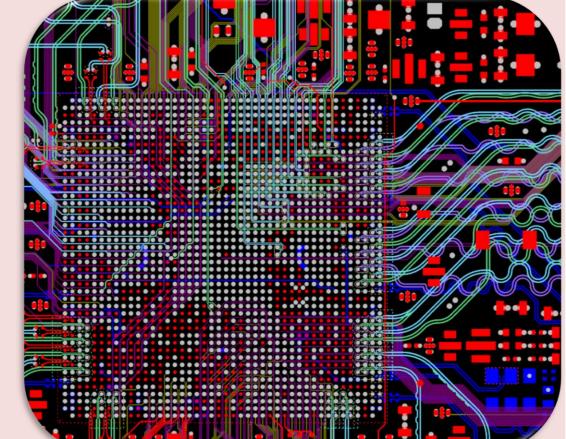

**FPGA**

# Challenge of Designing PCBs with complex FPGA and very high speed links

O. Auberson<sup>1</sup>, G. Curchod<sup>1</sup>, G. Habegger<sup>1</sup>, E. Messerli<sup>1</sup>, Ch. Keller<sup>2</sup>, N. Felber<sup>2</sup>, L. Monat<sup>3</sup>

<sup>1</sup>HES-SO/HEIG-VD, <sup>2</sup>IIS-ETHZ, <sup>3</sup>idQuantique SA

## **Challenge of Designing Complex PCBs**

26 Cu Layers PCB

High power supplies - up to 40 A

26 power supplies, 18 internal planes

Thick board versus Thin vias

Backdrilled vias

Routing FPGA with 2'000 pins

Very high speed signals up to 10 GHz

Controlled-impedance differential pairs

Stackup PCB V1

**FPGA**

**PCB Stakup**

### Power distribution

#### Layer usage - Ideal

- Thick copper

- Thin prepreg: high capacitance

- Many short vias, vias in pads

#### Layer usage - Reality

- Symetric stackup: high current on top

- Thick copper thick prepreg: filled planes for thinner prepreg

# High speed signaling

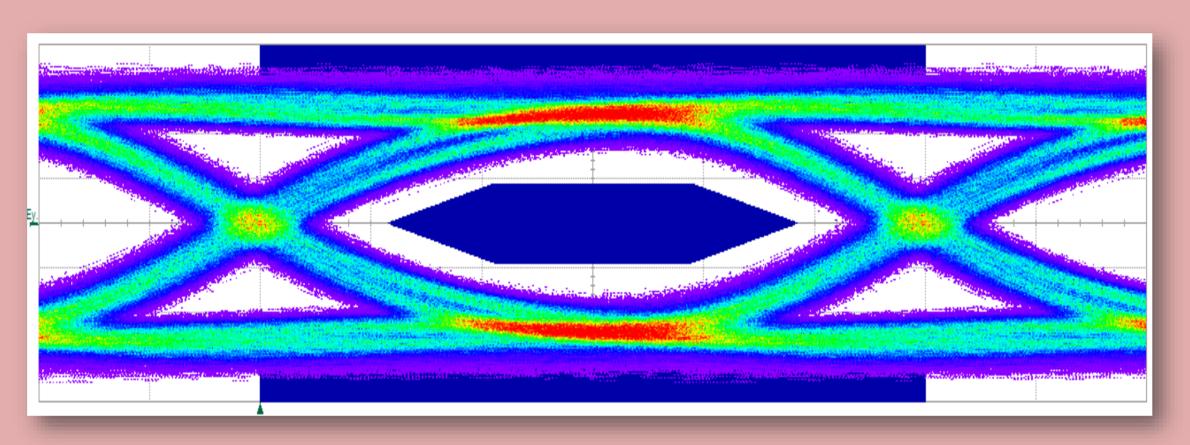

#### **PCB V1 Eye Measurements**

Eye measurement of a SFP+ transceiver

The measurement of the eye is made using a SFP+/SMA adapter plugged to a SFP+ connector of the QCrypt board and connected to two SMA inputs of the oscilloscope.

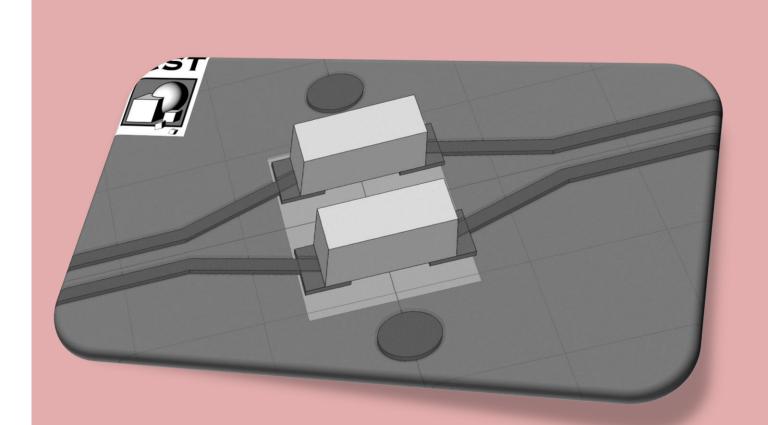

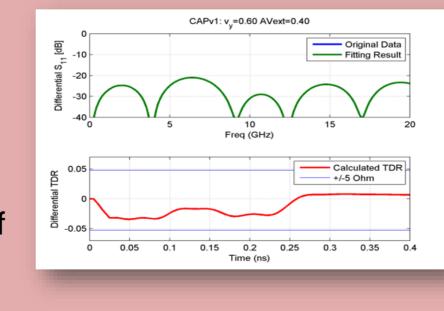

#### **PCB V2 3D Simulations**

#### Simulation of two capacitors in a differential highspeed connection

The capacitors are simulated as metal bricks. The curves show the optimal simulation result for the structure.

The green curve is the reflected energy. The red curve corresponds to a TDR measurement indicating the impedance deviation over the length of the line.

The 3D simulations have been carried on the CST STUDIO SUITE™.

# High density routing

- Narrow and wide differential lines

- Phase- and length-matched traces

- Via in pads

- Minimal vias of type snowman

- Space sharing of traces and decaps

- Clearance vs. low-res power planes

# History of PCB design and fabrication

PCB V1

PHOTOCHEMIE †

24 Cu Layers, asymetric

≥ 0.2mm Vias

PCB V2

WIKO †

26 Cu Layers, symetric

≥ 0.22mm Vias

Evaluation of more than 14 companies:

None without Redesign!

Total Height 2.71mm

Copper

Prepreg

Core

PCB V2

MicroPCB ✓

26 Cu Layers, symetric

≥ 0.25mm Vias

Total Height 3.3mm

Principal investigator: Nicolas Gisin (Nicolas.Gisin@unige.ch)

Contact: Etienne Messerli (etienne.messerli@heig-vd.ch)

Norbert Felber (felber@iis.ee.ethz.ch)