# **Cross-Layer Inexact Design for Low-Power Applications**

V. Camus<sup>1</sup>, G. Karakonstantis<sup>2</sup>, J. Schlachter<sup>1</sup>, A. Burg<sup>2</sup>, C. Enz<sup>1</sup>

<sup>1</sup> Ecole polytechnique fédérale de Lausanne (EPFL), Integrated Circuits Laboratory (ICLAB) <sup>2</sup> Ecole polytechnique fédérale de Lausanne (EPFL), Telecommunications Circuits Lab (TCL)

### Abstract

Achieving miniaturization, low-power and real-time data processing requires always more expensive design constraints and margins. Guard bands and worst case safety margins coupled with error correction units to ensure perfect calculations and robustness against Process-Voltage-Temperature (PVT) variations strongly deteriorate chip performance, power and cost efficiency.

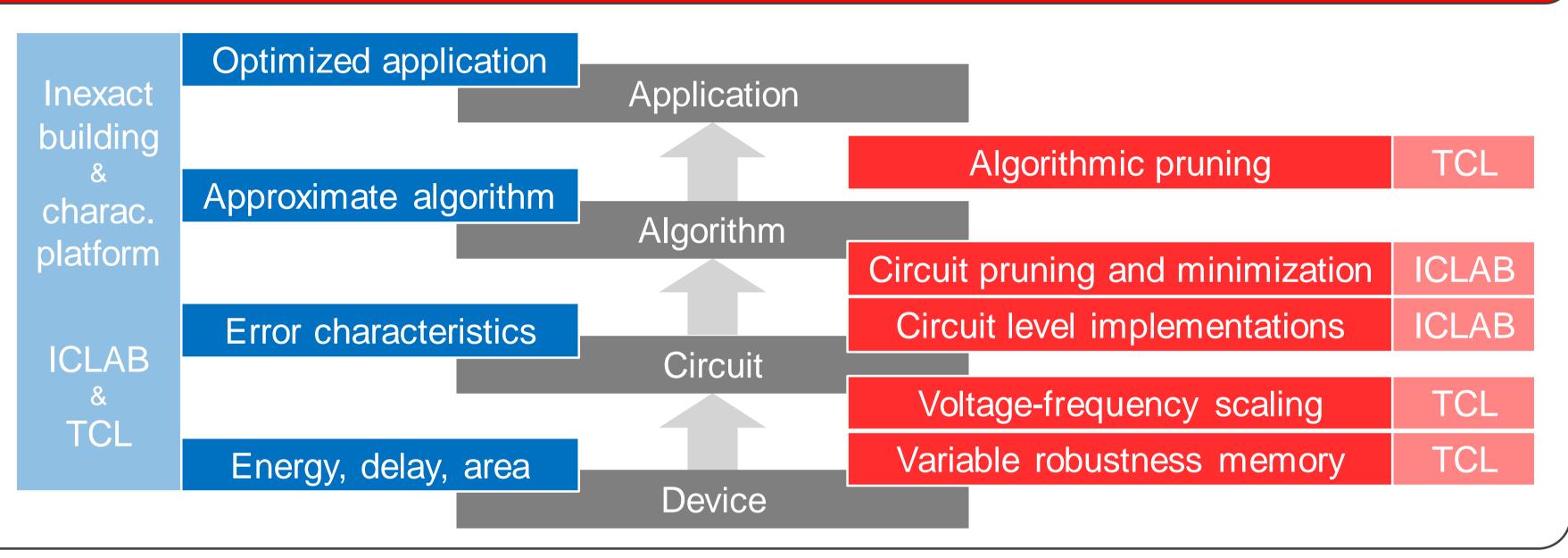

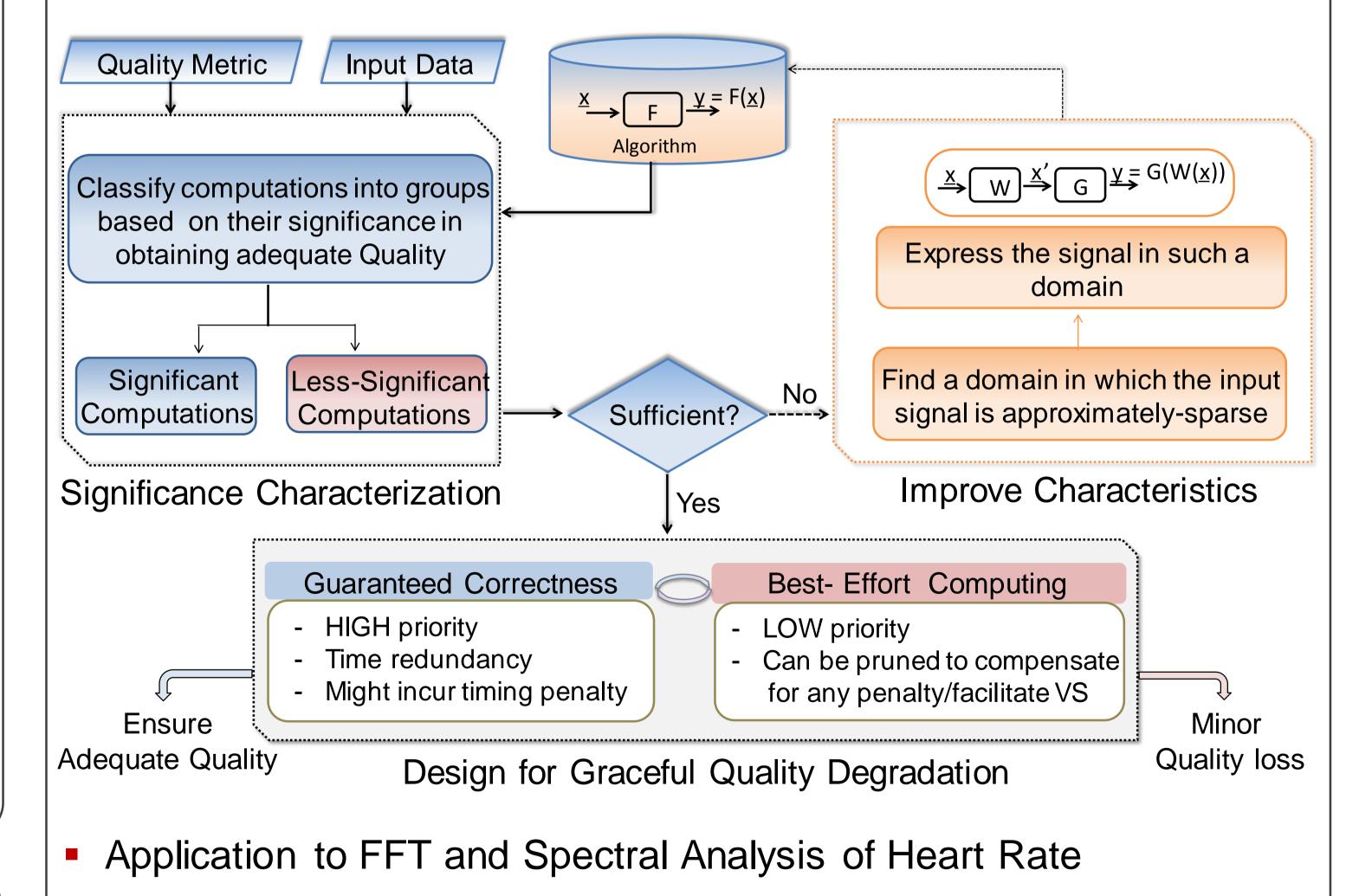

Approximate and error tolerant circuits are a radical new approach to trade calculation accuracy for better speed, power, area and yield. The IcySoC project platform revisits low-power and low-voltage VLSI design through a cross-layer combined inexact design framework.

#### Inexact characterization and co-design framework

Inexact design techniques used independently at any level of the system has been proved to lead to significant gains in energy efficiency. However, fully exploiting the potential of these techniques requires cross-level work to adapt to the desired application.

By joining forces in a bottom-up approach, two labs at EPFL collaborate in this project, combining their respective inexact design methodologies to a holistic framework for low-power design.

## **Circuit pruning and minimization**

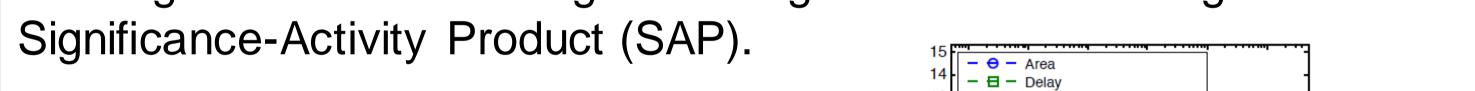

Pruning consists in deleting circuit's gates or cells having the lowest

## Algorithmic pruning

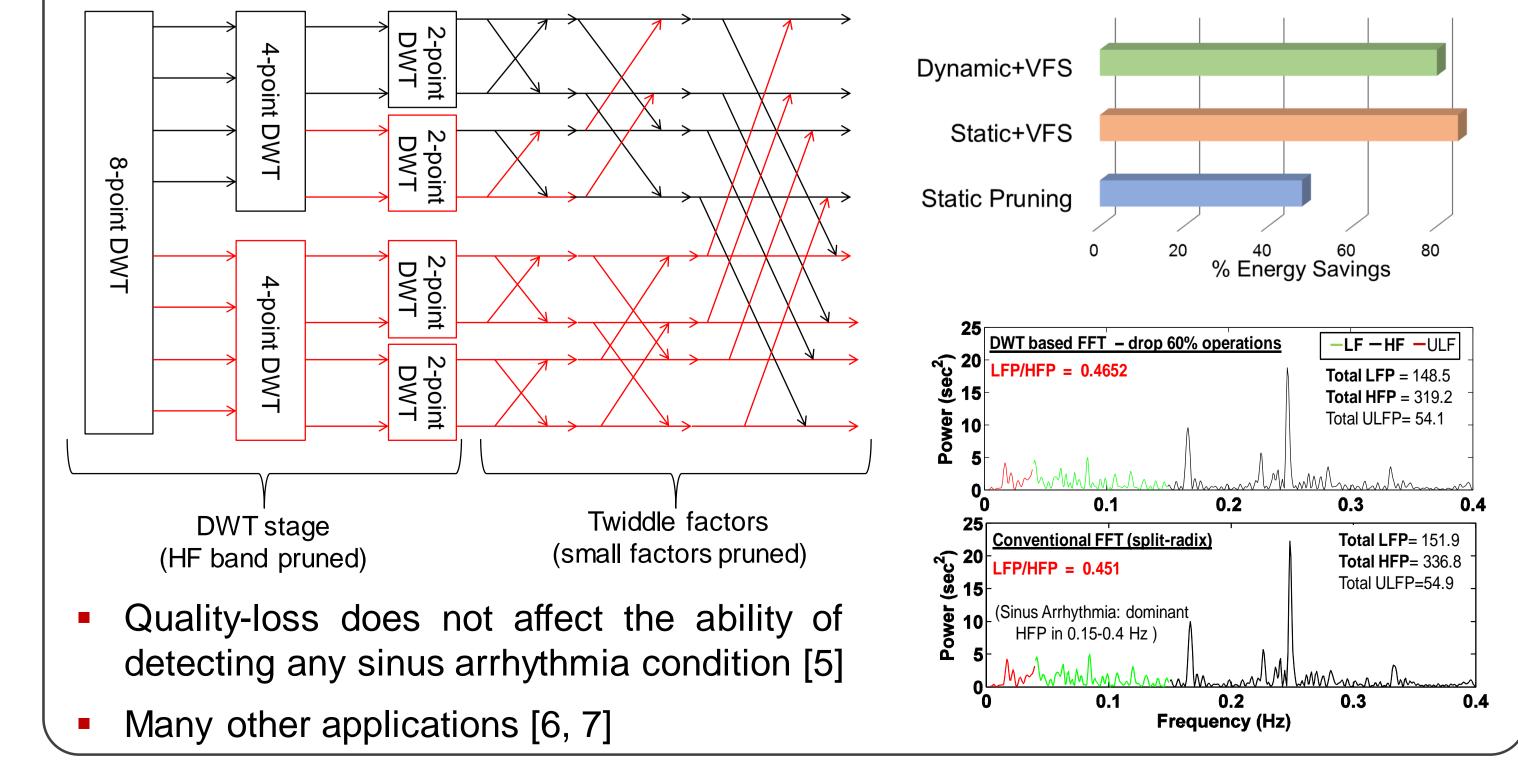

Pruning at the algorithm level consists of classifying the significance of computations and skipping the less-significant ones for adjusting to dynamically changing hardware capabilities and for saving power.

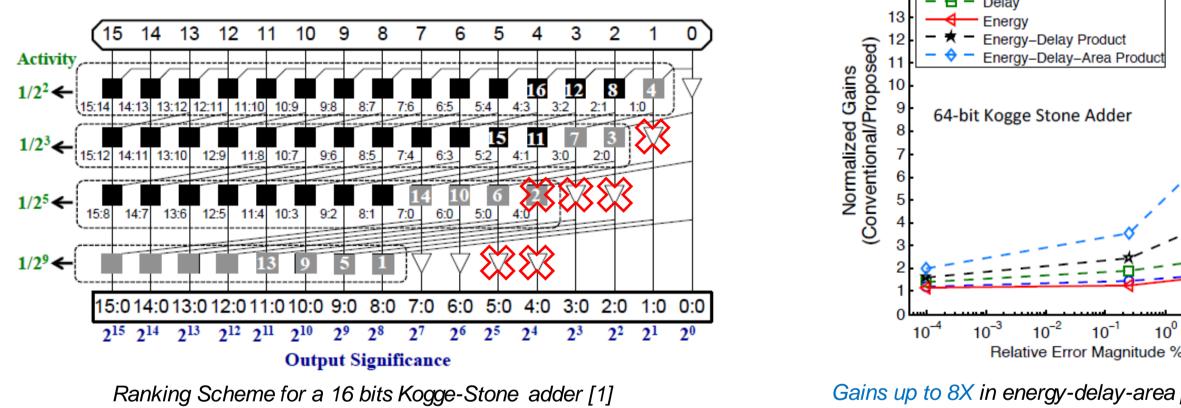

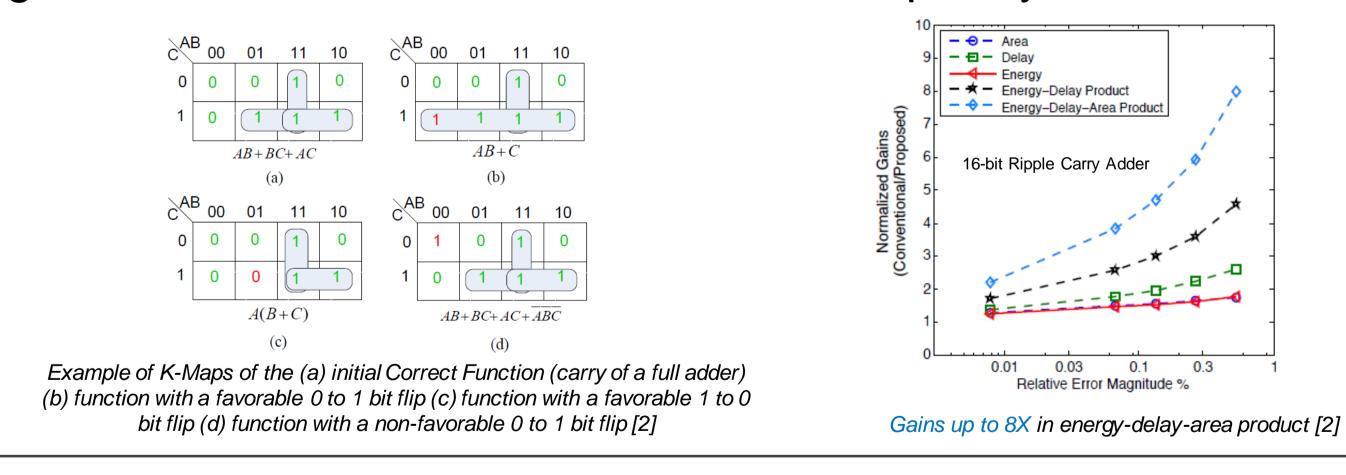

Gains up to 8X in energy-delay-area product [1]

Minimization consists in introducing bit flips in Karnaugh maps of logic functions in order to reduce circuit complexity.

## **Circuit level implementations**

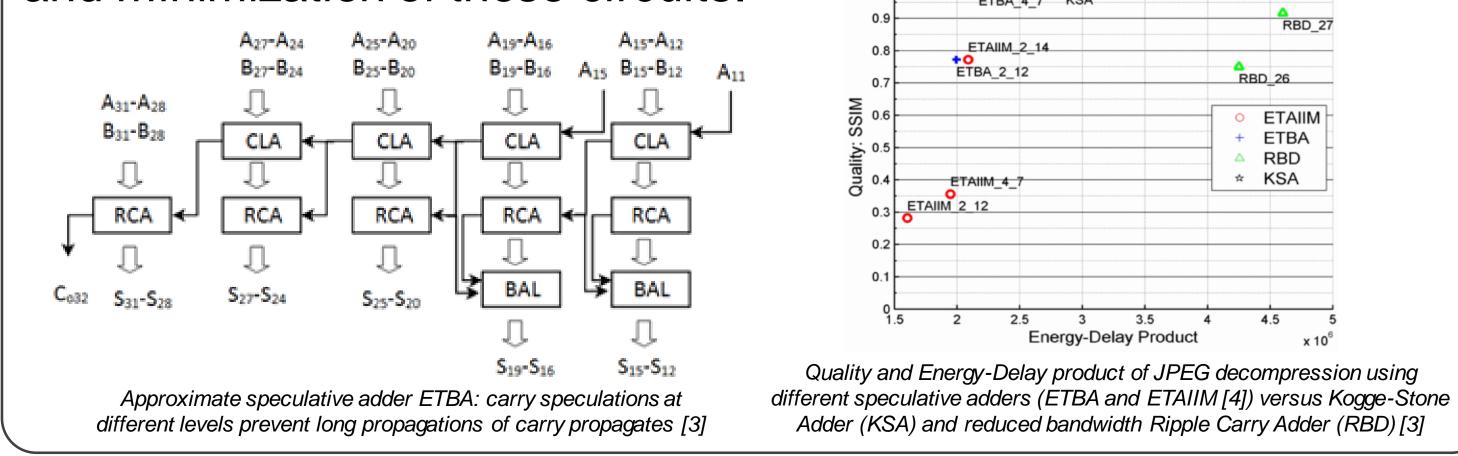

main idea in working at circuit level is The conceive to fundamentally different circuit schemes to better control the calculation error characteristics and allow more efficient pruning and minimization of these circuits. ETBA\_4\_7 KSA

[1] A. Lingamneni *et al.*, Algorithmic methodologies for ultra-efficient inexact architectures for sustaining technology scaling, *CF*, 2012. [5] G. Karakonstantis et al., A Quality-Scalable Spectral Analysis System for Energy-Efficient Health Monitoring, *DATE*, 2014. [2] A. Lingamneni et al., Parsimonious circuits for error-tolerant applications through probabilistic logic minimization, PATMOS, 2011. [3] M. Weber et al., Balancing Adder for error tolerant applications, ISCAS, 2013. [4] N. Zhu et al., An enhanced low-power high-speed Adder For Error-Tolerant application, ISIC, 2009.

[6] G. Karakonstantis et al., Process-Variation Resilient & Voltage-Scalable DCT Architecture for Robust Low-Power Computing, IEEE Trans. on VLSI Systems, 2010.

[7] G. Karakonstantis et al., On the Exploitation of the Error Resilience of Wireless Systems under Unreliable Silicon, DAC, 2012.