FÉDÉRALE DE LAUSANNE

# Fast and Scalable System Simulation Of Many-Core Heterogeneous SoCs

Shivani Raghav<sup>1,</sup> Martino Ruggiero<sup>1</sup>, David Atienza<sup>1</sup>,

Christian Pinto<sup>2</sup>, Andrea Marongiu<sup>2</sup>, Luca Benini<sup>2</sup>

<sup>1</sup>Embedded System Laboratory, EPFL, <sup>2</sup>Department of Electrical, Electronic and Information Engineering, University of Bologna,

### Motivation and Challenge

Demand for Hardware Acceleration (On Chip Many-Core Accelerators)

AMD Fusion (on-chip)

Hybrid Cores

Current simulation methods are sequential and slow

STHorm

IOw poweR Many-Core

**STmicroelectronics**

Heterogeneous

Coprocessors

1000

900

500

400 300 200

Need for a fast, parallel, scalable and inexpensive solution for simulation

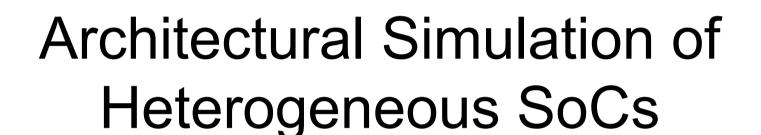

#### Solution – GPGPU Acceleration

#### Many-Core Single Node Accelerator **High Power** Switch TII M General Purpose CPU

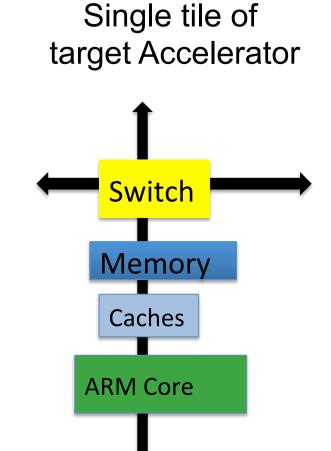

#### **Target Architecture**

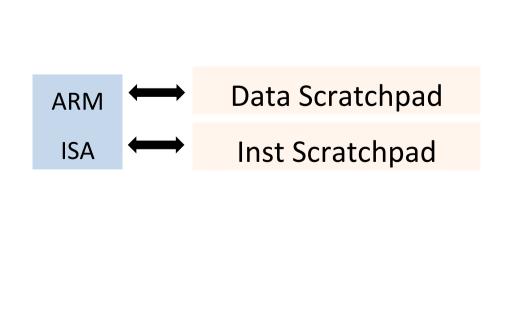

- Data-Parallel Coprocessors

- Simple In-order Cores

- RISC ARM and CISC x86

- 1000s of cores in a tile network

- Fine grain parallelism

#### **Simulation Features**

- Instruction Accurate

- Inexpensive and Easily Available

- Fast Development Cycle

- Portability (Target Independent)

- Interpretation based coresimulation

# Simulation Framework

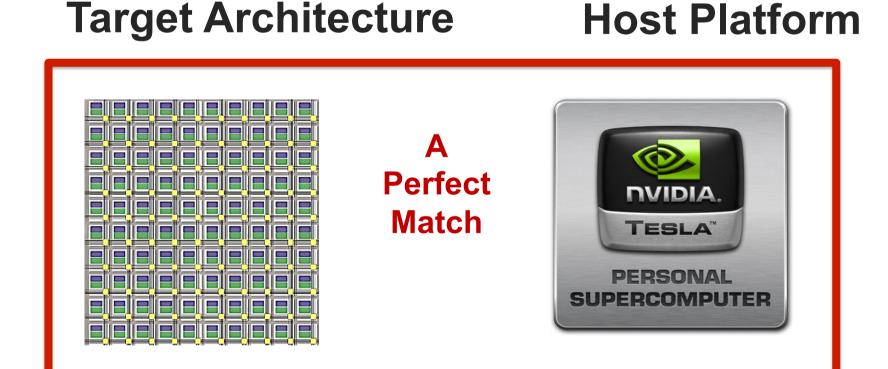

# Parallel Target → Parallel Simulator → Parallel Host

#### Experimental Results

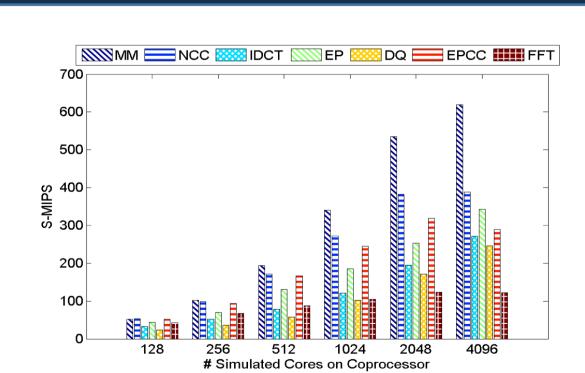

600 MIPS, 800x speed up from multicore host

# Simulated Cores on Coprocessor 50 MIPS, 350x speed up from multicore host

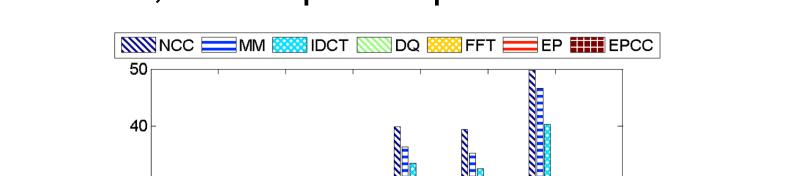

# Comparison with OVPSim

OVPSim – State-of-the-art parallel simulator on Multi-core Host ■ VISS-ARM ■ OVPSim Better simulation performance with increasing number of cores ~800x speed up Breakeven at simulation of 512 cores

## Conclusion

- Challenge and parallel simulator for heterogeneous SoCs

- Solution Parallelize 1000 core simulation using GPUs

- Design Full System Simulation using QEMU and SIMinG-1k

- Results High Scalability and speedup upto 4096 cores