swiss scientific initiative in health / security / environment systems

### ETH

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

# Novel MRI Platforms:

# Massive Data Acquisition and Processing for very high channel count distributed receivers Wearable MRI

Josip Marjanovic<sup>1</sup>, Jonas Reber<sup>1</sup>, David O. Brunner<sup>1</sup>, Klaas P. Prüssmann<sup>1</sup>

<sup>1</sup>Institute for Biomedical Engineering, University and ETH Zürich, Zürich

### Motivation

We aim at enhancing existing and enabling new methods in magnetic resonance imaging (MRI) signal acquisition and processing such as scan acceleration, improved signal quality and more patient comfort by building high-channel count in-bore receiver electronics and massive data aquisition and processing units.

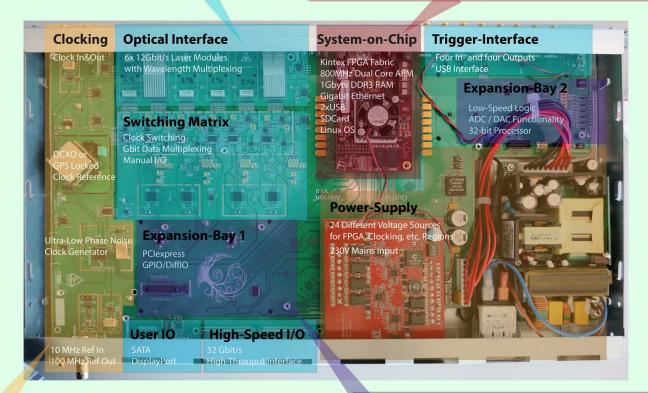

## **Design Overview**

In order to collect and preprocess the data stream from the high channel count arrays the previously introduced data acquisition unit has been significantly expanded in its capabilities. The chosen architecture provides ample real time processing power for handling massive arrays as well

as for future use in real-time accelerating tasks such as feedback of field measurements, motion detection and correction, fast channel combinations etc.

First images have been recorded using this new platform.

### High Bandwidth Optical Reception/Transmission

The system hosts 4 x 12 Gbps Receive and 2 x 12 Gbps Transmit optical modules which can be connected to existing magnetic field compatible FPGA boards. Those boards can be used in conjuction with two 8-channel ADC boards offering a total count of 4 x 16 channels. However, it is designed to operate in parallel with further out-field receiver modules scaling the channel count accordingly. The same FPGA boards can be used as nodes to collect the data from several recently developed ASICs replacing the existing ADC boards.

#### **Massive Data Processing System**

The digital processing system is based on a Xilinx® Zynq®-7045 module hosting a 800 MHz dual-core ARM® processor and a Kintex®-7 FPGA. It is a powerful computing engine suitable for hardware accelerated, realtime and massive data processing. It is the module where all peripheral interfaces, high-speed optical modules and the high-bandwidth NI FlexRIO® interface are gathered together.

### High-precision low-jitter clocking & synchronization

The unit hosts a high-precision oscillator clock with the possibility of GPS and external phase/frequency locking providing the reference clock which is distributed to the entire system as well as highly synchronized trigger I/O.

#### **Extensions and Peripherals**

The system supports a variety of extensions and perpheral interface standards such as SATA, HDMI, USB, Ethernet, PCIe and general purpose IOs. The outfield receiver system interfaces further primarily to a NI FlexRIO® system. However, the system can opperate fully autonomously.