Addressing safety-criticality in optimal deployment of data-flow applications onto many-core platforms

Stefanos Skalistis and Alena Simalatsar

**Motivation**

Rigorous System Design Laboratory (RiSD), EPFL

**Safety-critical systems**

Increasing processing demand  $\rightarrow$  Multi-/Many-Cores

Affected by scheduling, mapping and buffer sizes

Estimating Worst-Case Execution Times (WCET) of

parallel executing tasks is challenging:

Interferences due to accessing shared resources

**Application Model**

- Dataflow applications as SDF + with known guarantees

- + High degree of data and task parallelism

- + Known Worst-Case Computation (WCCT) time in isolation

# Background

## **Architecture Model**

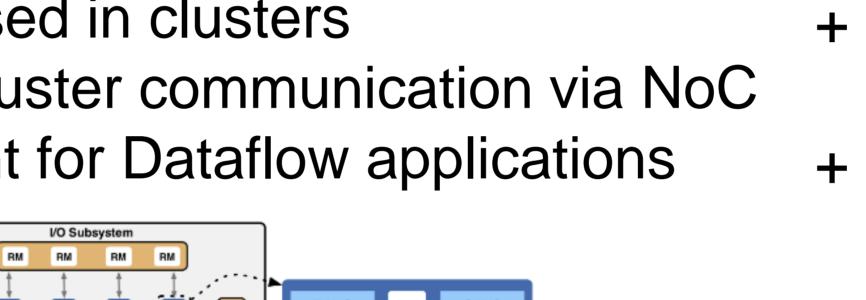

- + Large number of cores (>100) organised in clusters

- Intra-cluster communication via NoC

Setup:

Efficient for Dataflow applications +

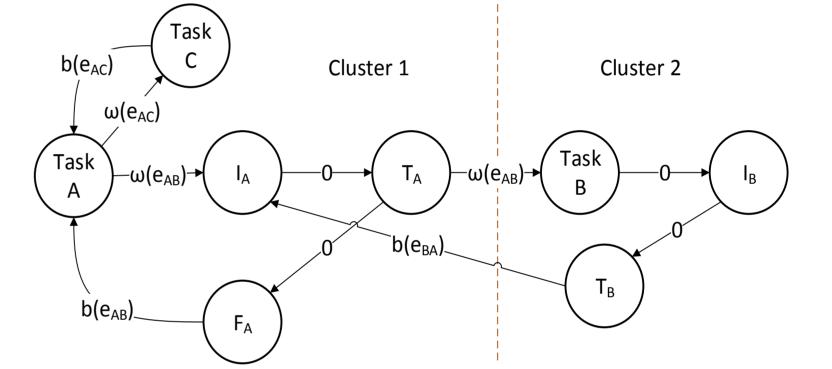

## **Unified System Model**

- + Derived from Application and Architecture model

- + Models both computation and communication system behavior

- + Basis for deriving WCET

Safe, optimal <u>scheduling requires knowledge of WCET</u>

WCET

**Vicious cycle**  $\rightarrow$  Safe and optimal deployment is hard!

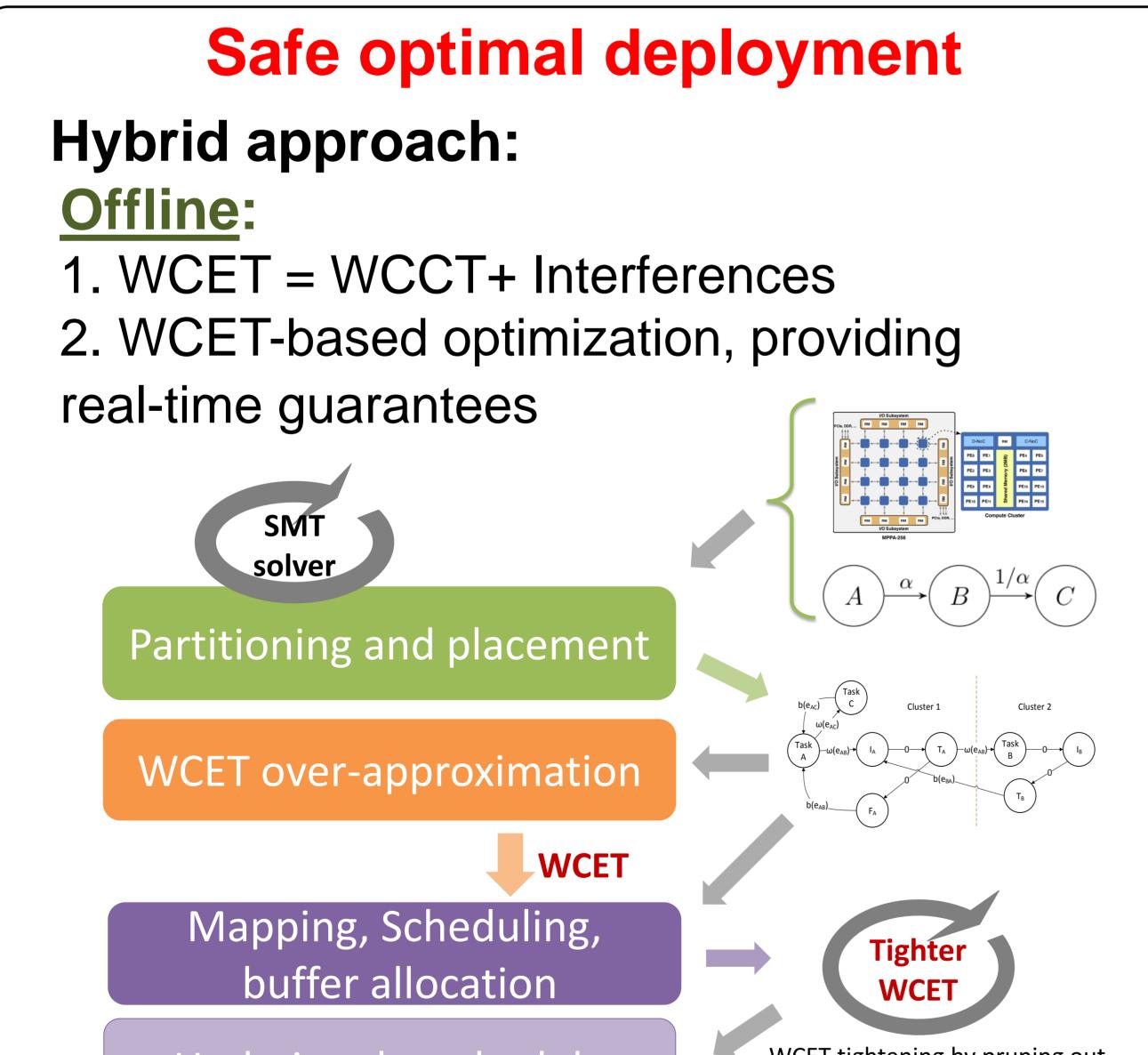

### Results

- StreamIT: 18 benchmarks with profiled WCCT

- After applying our approach, deployed on Kalray MPPAlacksquare256 chip (256 cores @ 400Mhz)

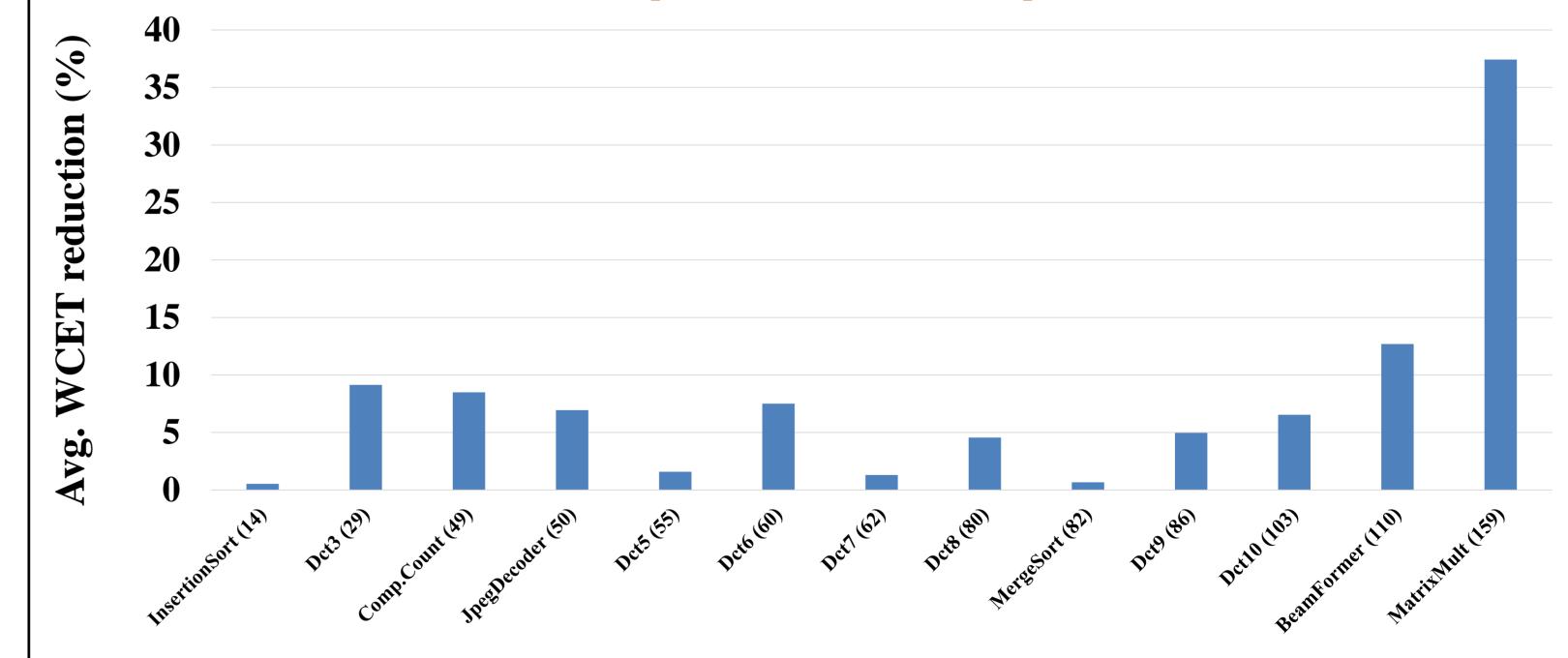

#### WCET improvement up to 37%

WCET tightening by pruning out interferences non overlapping tasks (neither in space nor in time) Offline

Online

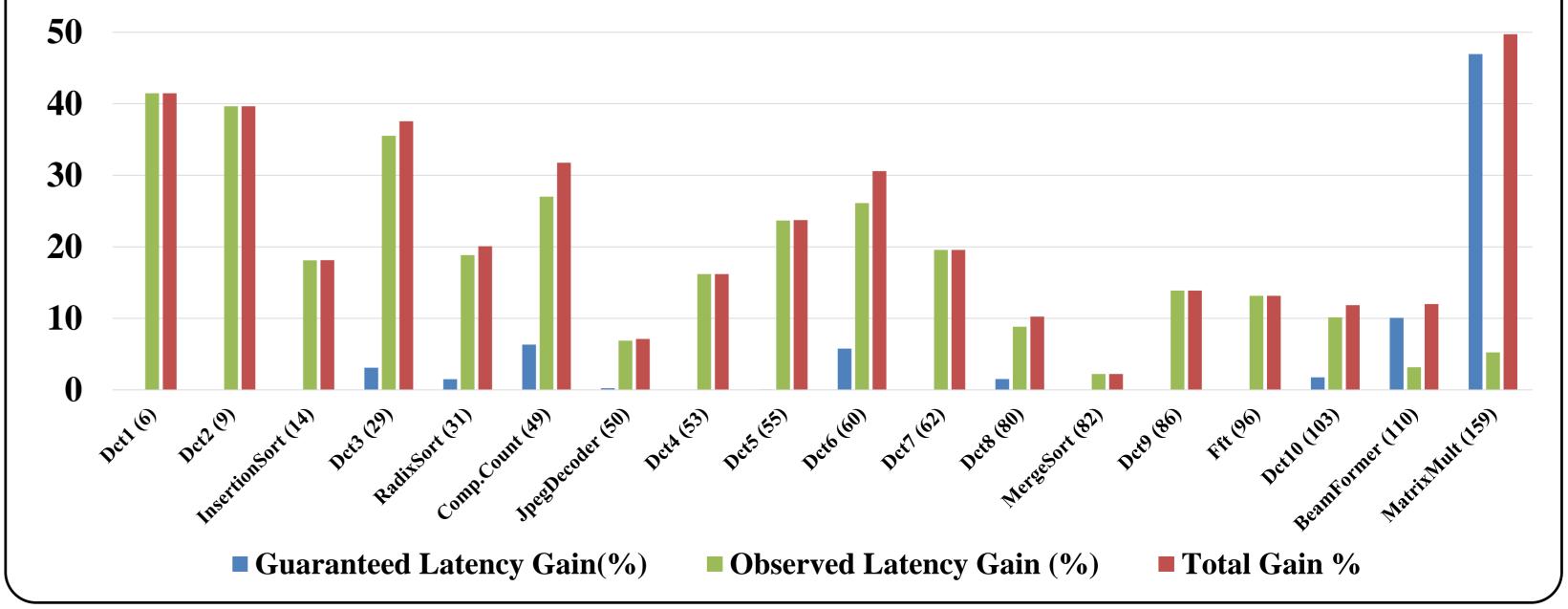

#### Updating the schedule

**Run-time optimization**

#### **Online:**

**Optimizations** based on actual execution times

Safe deployment without undermining performance

#### **Offline+online latency gain up to: 49%**

[1] Tendulkar, Pranav, et al. "Many-Core Scheduling of Data Parallel Applications using SMT Solvers." Digital System Design (DSD), 2014 17th Euromicro Conference on. IEEE, 2014. [2] De Dinechin, Benoît Dupont, et al. "Time-critical computing on a single-chip massively parallel processor." Design, Automation and Test in Europe Conference and Exhibition (DATE). IEEE, 2014.